TIE-E Plus Contest Regulation

- General

The present document outlines the primary factors to consider prior to and after enrollment in the TIE-E Plus competition. We would kindly ask you to read it thoroughly and for any questions you may have that are not directly addressed in the following lines you can always reach up to us at tieplus@up-see.org, and one member in the organizing committee will get back to you as soon as possible. We are dedicated to ensuring your successful participation at the event and facilitating your up-skilling process within our virtual prototyping community.

- Brief description

TIE-E Plus Contest is a prestigious competition established by industry professionals in collaboration with academia, with the main goal of driving froward innovative practices in engineering education, particularly focused on product virtual prototyping methods and techniques.

Our objective is to help you understand current industry challenges and support you in becoming the engineer of tomorrow. We look to achieve this by exposing you to the latest technologies and industry product requirements. Thus, TIE-E Plus draws inspiration from real-life engineering challenges brought up by our industry partners and has as main goal to give you the chance to evaluate your engineering skill set against actual electronic product development challenges.

- Contestant profile requirements

The contestant must be enrolled at a higher education institution. Accepted profiles will fall under one of the following categories:

- Undergraduate students

- Graduate students

- Master’s students

- PhD Students

All applications will be verified by the organizing committee members. As soon as that happens you will get notified of the status of your application.

Besides that, the contestant shall have a minimum idea about the contest’s scope and show at least basic skills using the tools needed to solve the proposed subject.

Knowledge of English language (B1 level at least) is mandatory, as the subject presentation, trainings, and final report are/shall be written in English.

- Workflow

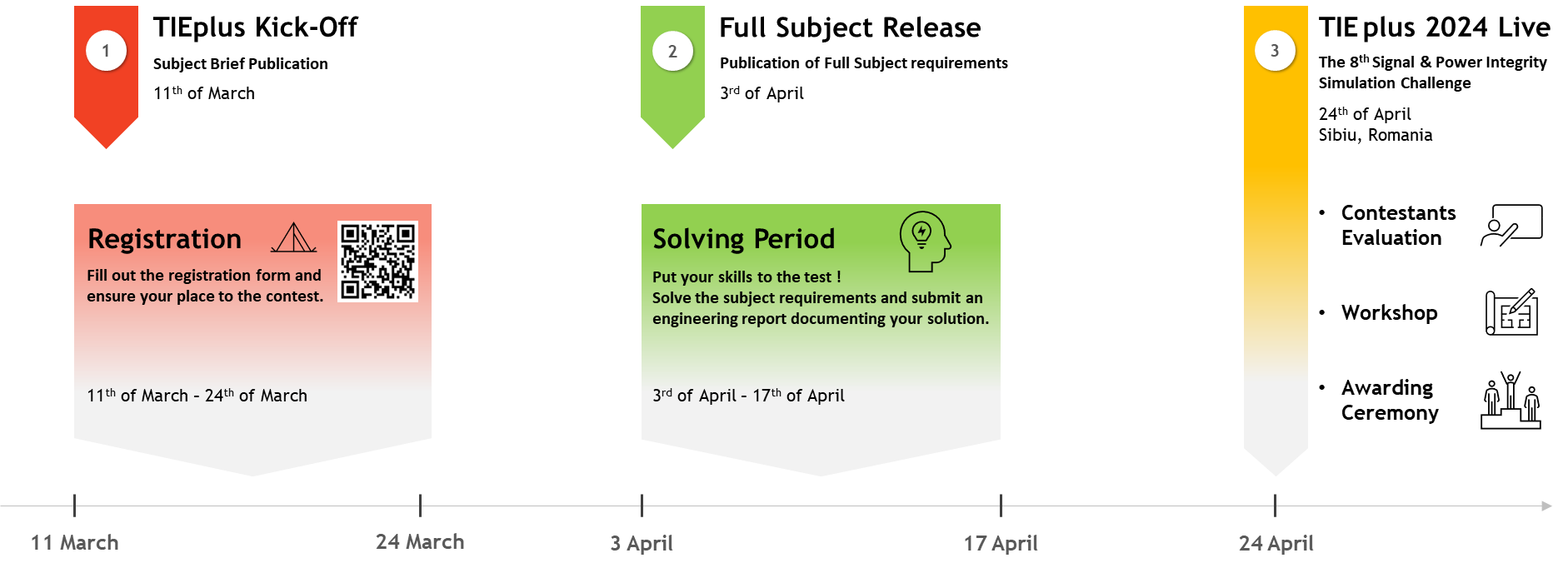

Further, a step-by-step guide for registering will be presented.

- First, identify the section you want to register to: Signal and Power Integrity, Thermal Management or Structural Analysis

- Fill in the registration form with the requested information.

- An acceptance or rejection notice will be sent to you.

- You will receive in your acceptance email the links to the specific group for your section. Please register and join the indicated group.

- During the solving period you’ll have access to a database of knowledge prepared by the technical committee members and a series of workshops. Feel free to join discussions and debates related to the subject.

- Solve the subject and create a report, considering the guidelines of each subject. Please remember that the quality of the report plays a major role in the evaluation.

- Upload the finished report and wait for our notification to see if you qualify to the next phase.

- Finalists will give a brief presentation on the 24th of April, live, in Sibiu, where they shall defend their approach, with arguments and examples, debating together with the committee.

Please be aware that the quality of your presentation plays a major role in the overall final evaluation. The preliminary results after the initial report analysis may change drastically after the final presentation.

We encourage collaboration and discussions with academic coordinators or other peers, yet we do not tolerate cheating. Do not upload a solution that was not developed by you, as we will find out later, during live presentations.

Good luck!