#### **TIEplus 2019 Subject**

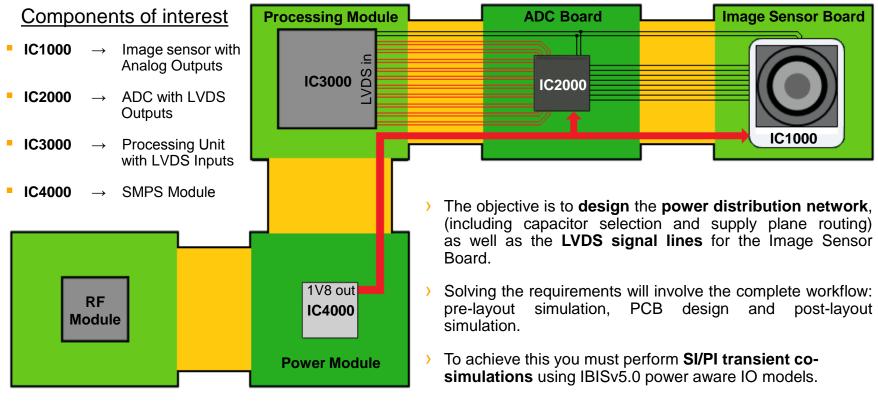

## TIEplus 2019 Subject Block Diagram

The diagram below describes a simplified architecture of a space cube satellite PCB which is divided in 5 functional modules: RF, Power, Processing, ADC and Image Sensor.

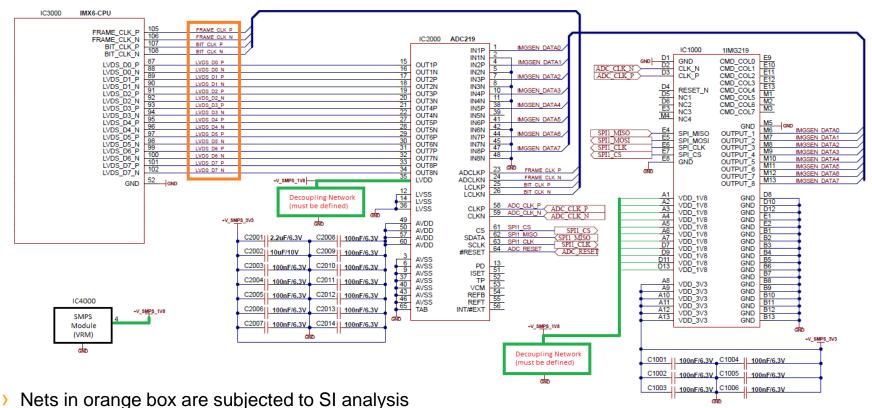

### **TIEplus 2019 Subject** Schematic

Green boxes represent the capacitor decoupling networks that result form the PI design

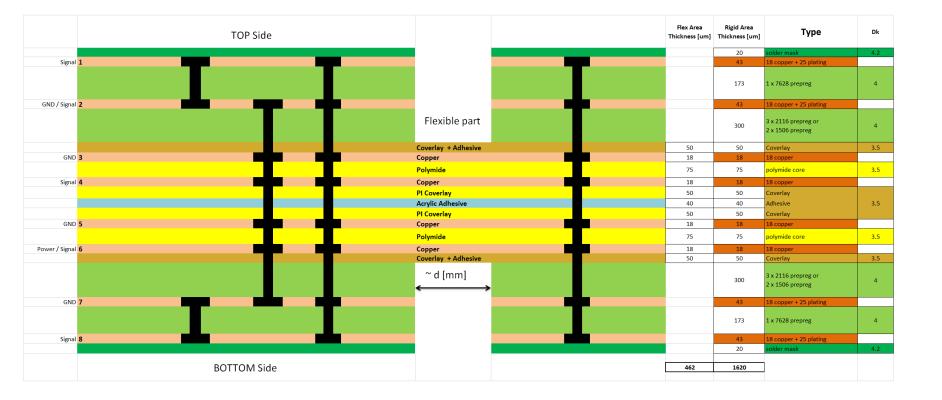

#### TIEplus 2019 Subject Stack-up

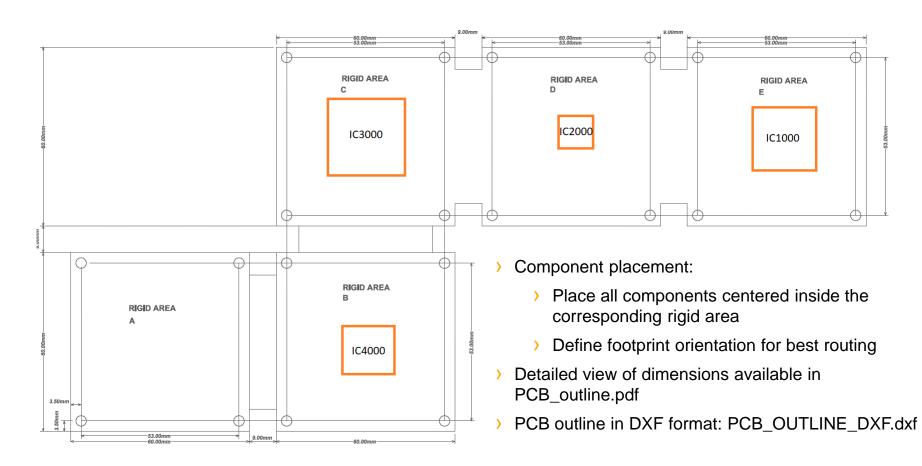

#### **TIEplus 2019 Subject** PCB Outline

# **TIEplus 2019 Subject** Modeling data

| Model                     | File                 | Description                                           |

|---------------------------|----------------------|-------------------------------------------------------|

| IC1000 on-die capacitance | ic1000_on-die_cap.sp | Image sensor internal decoupling capacitance          |

| IC2000 ibis model         | ic2000.ibs           | ADC power aware IBIS model<br>for LVDS output buffer  |

| IC2000 on-die capacitance | ic2000_on-die_cap.sp | ADC internal decoupling capacitance                   |

| IC3000 ibis model         | ic3000.ibs           | Processing module IBIS model<br>for LVDS input buffer |

| IC3000 package model      | lc3000_pkg.s40p      | Processing module PCB parasitics for LVDS lines       |

| IC4000 VRM model          | VRM_model.sp         | Power supply model                                    |

Capacitor models can be downloaded from Murata website (GCM series):

- > https://ds.murata.co.jp/simsurfing/mlcc.html?lcid=en-us OR

- > <u>https://psearch.en.murata.com/capacitor/result/smd/?pid=GCM&pid\_method=begin&cat=lineup&status=development</u>

# **TIEplus 2019 Subject** Requirements

- > Design the LVDS channel IC2000->IC3000 to meet signal integrity requirements

- > Define controlled impedance routing guidelines

- > Define length matching requirements

- > Evaluate termination scheme

- Design the power delivery network for 1V8 power rail in order to meet specifications of supply voltage IC1000 and IC2000

- > Evaluate power rail IR Drop and define power plane routing guidelines

- > Define worst-case noise budget at IC power pins (in dynamic current conditions)

- Define decoupling capacitor network considering the simultaneous switching of all IC2000 LVDS outputs

- > Route the power delivery network (including capacitors) according to findings

- Based on previous findings route the LVDS interface and the power delivery network (including capacitors) for the 1V8 power rail

- > Perform post-layout transient SI-PI co-simulation to validate design and optimize if required

\* Pre-layout SI-PI transient co-simulation is required in order to accurately evaluate power supply noise and impact on LVDS signal parameters