## **TIEplus 2018 Subject**

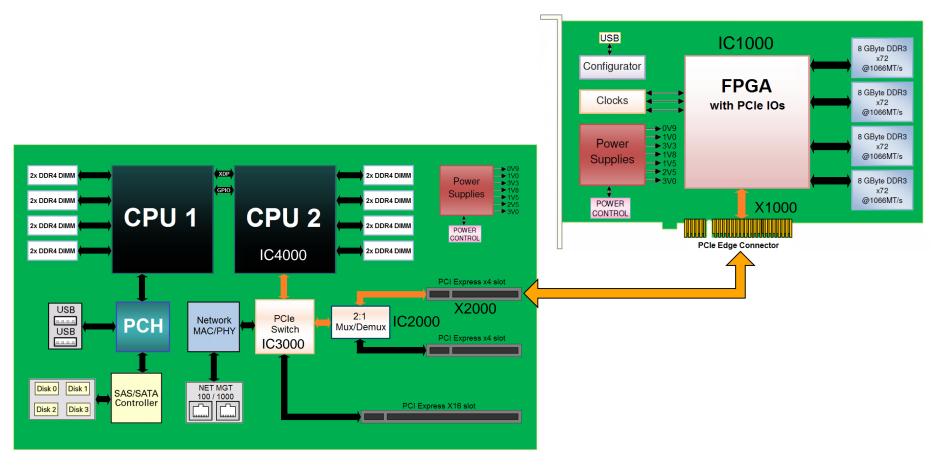

The diagram in slide 2 describes the simplified architecture for a FPGA graphic accelerator card connected to a server motherboard by a standard PCIe\* edge connector (slot).

System components for the PCIe channel (marked in orange color):

- IC1000  $\rightarrow$  FPGA with PCIe I/O

- X1000  $\rightarrow$  board edge connector

- X2000  $\rightarrow$  socket connector for PCIe

- IC2000  $\rightarrow$  PCIe multiplexer IC

- IC3000  $\rightarrow$  PCIe switch IC

- IC4000  $\rightarrow$  CPU with PCIe I/O

## Requirements:

- 1) Define full channel PCIe routing recommendations for the FPGA graphic accelerator card and server motherboard based on pre-layout transient simulation

- 2) Route the PCIe interface for the FPGA graphic accelerator card and server motherboard PCBs in a dedicated CAD environment

- 3) Verify channel compliance to PCIe standard by using s-parameter extraction (postlayout)

- 4) Verify impact of random jitter on differential signaling timing parameters

\*PCIe (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e is a high-speed serial computer expansion bus standard.

## **TIEplus 2018 Subject**