# **1. General description of the project:**

The purpose of this project is to design one prototype satellite which will be part of a much larger network of such devices, placed temporarily on earth's orbit, for close monitoring of the permafrost (in and around the Arctic and Antarctic regions).

The schematic of the proposed project is indicated in Annex\_1.

#### The system description is as following:

In order to perform its main function, that of sequential photography, this device is using an ultra-high resolution, 71 Megapixels CMOS image sensor. This sensor will acquire 3 frames/second, every 6 hours, in order to completely capture one full seasonal climate cycle. The device is made up from the following components:

- ➔ The 71 megapixel CMOS image sensor. This component will be used at it's technological limit, to aquire 3 frames per second, in order to filter the noise per photo as much as possible (images will be processed locally and only one will be stored).

- ➔ In order to properly manage all the information which is fed via the image sensor, the chosen processing unit will be a system-on-module (SoM) IMX6-CPU has the following specifications:

- -528MHz NXP i.MX 6UL/6ULL ARM Cortex-A7 Processors

- 512MB DDR3 SDRAM

- 256MB Nand Flash (4GB eMMC Flash is optional)

- Ready-to-Run Linux 4.1.15

- → One RadioFrequency(RF) module used for high frequency communications. The satellite constellation will be comprised of 20 satellites which will be linked all together.

- → One Power Management IC(PMIC), will handle all the necessary energetic distribution needs.

- → Due to recyclability reasons, easy handling and fast access, the satellite was designed to permit access to its internal data storage device (*eMMC*) from someone/something directly in outer space (most probably with ISS) for data management. The link to the data lines will be handled via an adapter tool connecting directly to one cluster of test points.

#### 2. General requirements:

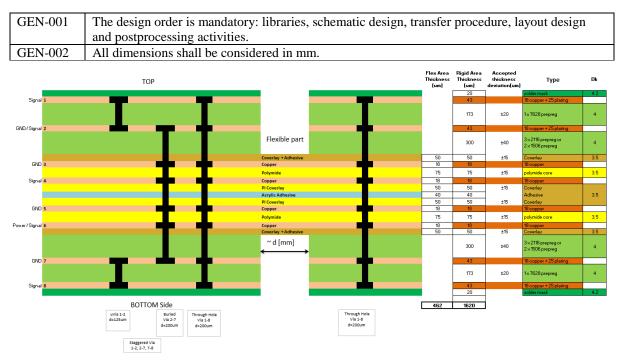

Figure 1. Proposed stack-up definition for the thermal monitoring system.

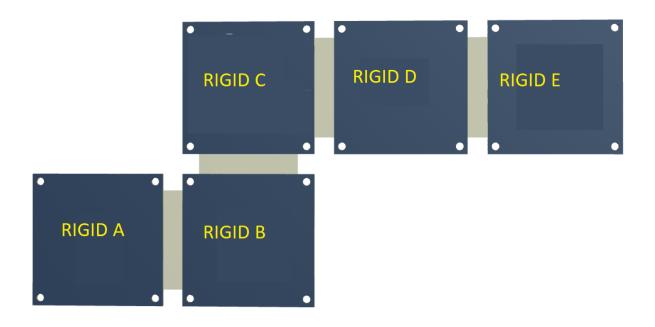

Due to the complexity of this monitoring unit, and the geometry of the housing, the unit must be designed using one *rigid-flex PCB*. It contains *5 rigid sides* named intuitively **A**, **B**, **C**, **D** and **E**. Each one of these sides has its specific constraints and placement requirements. See *Annex\_2* and *Annex\_3*.

## **3. Schematic design specifications:**

| SCH-001 | The schematic project will be created using any CAD system accepted in the contest (and           |

|---------|---------------------------------------------------------------------------------------------------|

|         | respects all the minimum requirements published on the TIE official website).                     |

| SCH-002 | The required components will be created in a new library named <b>TIE2019</b> .                   |

| SCH-003 | The schematic must be drawn in a clear manner, e.g.: all references and values must have          |

|         | proper size and orientation, un-necessary crossings shall be avoided, no overlap of texts,        |

|         | graphical elements and electrical objects is allowed.                                             |

| SCH-004 | The schematic must be electrically correct, clean and readable. All reference designators must    |

|         | strictly follow Annex_1. The main purpose is to generate a correct netlist for PCB design, but it |

|         | must also provide a clear representation of functionality.                                        |

| SCH-005 | Test pads must be placed on the following nets (2 test pad per net): +V_SMPS_1V8,                 |

|         | +V_SMPS_3V3, +V_LDO_RF_3V3, +V_IN and GND.                                                        |

|         | Testpoints will be placed also on the high speed lines connecting the eMMC to the iMX-6           |

|         | system on module (eMMC_CMD, eMMC_RST, eMMC_CLK, eMMC_DS,                                          |

|         | <i>eMMC_DATA07</i> ).                                                                             |

| SCH-006 | Following completion of the schematic, a <i>Bill of Material (BOM)</i> must be generated in       |

|         | following formats: .xlsx .pdf .txt .csv.                                                          |

| SCH-007 | The same page size shall be used as the one received in <i>Annex_1</i> .                          |

# 4. Layout design specifications:

#### Figure 2. 2D view of the PCB and specific area naming.

| PCB-001       The PCB layout design will take into consideration the proposed stack-up from <i>Figu</i> participant should define in their individual CAD software <i>only the rigid stack-up</i> . N trace width is <i>0.070mm</i> and minimum clearance is <i>0.100mm</i> .         PCB-002       Signal routing will be done as stated in the stack-up definition table/file provided. <i>PL</i> |                                                                                                         |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                         |  |  |  |  |

| PCB-002 Signal routing will be done as stated in the stack-up definition table/file provided <b>Pl</b>                                                                                                                                                                                                                                                                                              |                                                                                                         |  |  |  |  |

| attention to the indications regarding the power plane distribution routing, signal of                                                                                                                                                                                                                                                                                                              |                                                                                                         |  |  |  |  |

| layers and the routing in the flexible areas. See Annex_3.                                                                                                                                                                                                                                                                                                                                          |                                                                                                         |  |  |  |  |

| PCB-003 Component descriptions, including standard footprints are indicated in the provided s<br>and all the designers should have almost all of them prepared before the contest. One                                                                                                                                                                                                              | single                                                                                                  |  |  |  |  |

| component must be created as specified in the provided datasheet and saved in the T                                                                                                                                                                                                                                                                                                                 | IE2019                                                                                                  |  |  |  |  |

| library alongside all the components. For clarifications see Annex_5.                                                                                                                                                                                                                                                                                                                               |                                                                                                         |  |  |  |  |

| PCB-004 All VIAs will have the following properties:                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |  |  |  |  |

| • THT VIA (usage for rigid and flexible areas): 200µm hole diameter, 350µm                                                                                                                                                                                                                                                                                                                          | <b>n</b> solder                                                                                         |  |  |  |  |

| mask opening and <b>400µm</b> copper pad;                                                                                                                                                                                                                                                                                                                                                           |                                                                                                         |  |  |  |  |

| Blind/Buried VIAS (only rigid):                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                         |  |  |  |  |

| • Layer 1 => Layer 2 – Blind(micro) via 125um hole size, pad size 325um                                                                                                                                                                                                                                                                                                                             | , no solder                                                                                             |  |  |  |  |

| mask opening;                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                         |  |  |  |  |

| • Layer 2 => Layer 7 - Buried via 200um hole size, pad size 500um;                                                                                                                                                                                                                                                                                                                                  |                                                                                                         |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>Layer 7 =&gt; Layer 8 – Blind(micro) via 125um hole size, pad size 325um, no solder</li> </ul> |  |  |  |  |

| mask opening;                                                                                                                                                                                                                                                                                                                                                                                       | ,                                                                                                       |  |  |  |  |

| PCB-005 In order to have the desired functionalities, the components must be precisely placed                                                                                                                                                                                                                                                                                                       | 88                                                                                                      |  |  |  |  |

| indicated in the mechanical documentation. See <i>Annex_2</i> .                                                                                                                                                                                                                                                                                                                                     | , <b>u</b> 5                                                                                            |  |  |  |  |

| PCB-006 The PCB origin shall be placed in the middle of the <i>tooling hole No1</i> . See <i>Annex_2</i> .                                                                                                                                                                                                                                                                                          |                                                                                                         |  |  |  |  |

| PCB-007 Knowing the mechanical information given in <i>Annex</i> _2, please define the routing/pl                                                                                                                                                                                                                                                                                                   |                                                                                                         |  |  |  |  |

| restrictions on the specific mechanical/restriction layers accordingly (layer assignation                                                                                                                                                                                                                                                                                                           |                                                                                                         |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                     | 11 15                                                                                                   |  |  |  |  |

| described in the Annex_2).PCB-008Minimum distance between two adjacent components is 400µm (component outline)                                                                                                                                                                                                                                                                                      | to                                                                                                      |  |  |  |  |

| 5 1 1 1                                                                                                                                                                                                                                                                                                                                                                                             | 10                                                                                                      |  |  |  |  |

| component outline), and pad to pad 250μm.                                                                                                                                                                                                                                                                                                                                                           |                                                                                                         |  |  |  |  |

| PCB-009 On flexible areas, due to manufacturing requirements the routing will be done with <i>r</i>                                                                                                                                                                                                                                                                                                 |                                                                                                         |  |  |  |  |

| traces. Also, if layer transitions are needed (via usage is mandatory) it is absolutely a                                                                                                                                                                                                                                                                                                           | must to                                                                                                 |  |  |  |  |

| use <i>teardrops</i> in order to prevent trace-to-via detachments.                                                                                                                                                                                                                                                                                                                                  |                                                                                                         |  |  |  |  |

| PCB-010The Camera Sensor (1IMG219) shall be placed as indicated in Annex_2.                                                                                                                                                                                                                                                                                                                         |                                                                                                         |  |  |  |  |

| PCB-011  | The RF Module shall be placed as indicated in <i>Annex_2</i> .                                                         |                  |                                |                |                  |                                       |                     |             |

|----------|------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------|----------------|------------------|---------------------------------------|---------------------|-------------|

| PCB-012  | Signal integ                                                                                                           | grity requ       | irements:                      |                |                  |                                       |                     |             |

|          | All relevant information regarding the specific trace routings are provided from TIE+                                  |                  |                                |                |                  |                                       |                     |             |

|          | contest results. The relevant requirements provided are as following:                                                  |                  |                                |                |                  |                                       |                     |             |

|          | 1. <u>For single ended traces</u> :                                                                                    |                  |                                |                |                  |                                       |                     |             |

|          | For correct                                                                                                            | ly determi       | ning the trace                 | width fo       | r eMMC tra       | aces please use t                     | he tool provid      | led in      |

|          | Annex_3. Pay close attention to the indications about the settings needed, before using the                            |                  |                                |                |                  |                                       |                     |             |

|          | calculator. <u>For p</u>                                                                                               | proving the      | e calculation,                 | please p       | rovide a sci     | eenshot from th                       | <u>te tool.</u>     |             |

|          |                                                                                                                        |                  | ngth for eMN                   |                |                  |                                       |                     |             |

|          |                                                                                                                        |                  |                                |                |                  | or stacked are a<br>nes to clock skey |                     |             |

|          |                                                                                                                        |                  |                                |                |                  | considered 3x tr                      |                     | <b>V</b> ); |

|          | 2. For                                                                                                                 | · different      | ial pairs:                     |                |                  |                                       |                     |             |

|          |                                                                                                                        |                  |                                |                |                  |                                       | T                   |             |

|          | 10001                                                                                                                  | Layers           | Reference                      | Trace<br>width | Trace<br>spacing | Spacing to                            | Spacing<br>to other |             |

|          | 100Ohm<br>Diff.                                                                                                        | Layers           | layers                         | [um]           | [um]             | GND [um]                              | nets [um]           |             |

|          | Pairs                                                                                                                  | 1/8              | 2/7                            | 200            | 230              | Min. 250                              | Min. 400            |             |

|          |                                                                                                                        | 4                | 3&5                            | 90             | 230              | Min. 250                              | Min. 350            |             |

|          |                                                                                                                        |                  |                                |                |                  |                                       |                     |             |

|          |                                                                                                                        |                  |                                | maximun        | n allowed t      | race-to-trace len                     | gth difference      | e) for      |

|          |                                                                                                                        | ines: <b>3mm</b> | ı;<br>ntial pair leng          | th for I V     | /DS· 120mr       | n.                                    |                     |             |

|          |                                                                                                                        |                  | -pair skew for                 |                | DS. 120111       | п,                                    |                     |             |

|          |                                                                                                                        |                  | CLK maximu                     |                |                  |                                       |                     |             |

|          |                                                                                                                        |                  | ata maximum<br>ver transitions |                |                  |                                       |                     |             |

|          | For differential                                                                                                       | pair routi       | ngs please be                  |                |                  |                                       | g symmetry,         | layer       |

| PCB-013  | transitions and return path! Power integrity requirements:                                                             |                  |                                |                |                  |                                       |                     |             |

| 1 CD-013 | All relevant information regarding the specific trace routings are provided from TIE+                                  |                  |                                |                |                  |                                       |                     |             |

|          | contest final results. The relevant requirements provided are as following:                                            |                  |                                |                |                  |                                       |                     |             |

|          | ➔ Minimum decoupling capacitors per pin/ pin cluster                                                                   |                  |                                |                |                  |                                       |                     |             |

|          | <b>For 1V8:</b> @ IC1000 (Im. Sensor) : $1 \ge 100$ F + $4 \ge 100$ nF                                                 |                  |                                |                |                  |                                       |                     |             |

|          | <ul> <li>@ IC2000 (ADC) : 1 x 10uF + 3 x 100nF</li> <li>➔ Minimum vias per capacitor pin:</li> </ul>                   |                  |                                |                |                  |                                       |                     |             |

|          | For 1V8: min 2 via/pin                                                                                                 |                  |                                |                |                  |                                       |                     |             |

|          | O 7mi O 30mi                                                                                                           |                  |                                |                |                  |                                       |                     |             |

|          | Y                                                                                                                      | I I              | 0                              |                |                  |                                       |                     |             |

|          |                                                                                                                        |                  |                                |                |                  |                                       |                     |             |

|          | E-COLOR -                                                                                                              | -                |                                |                |                  |                                       |                     |             |

|          |                                                                                                                        | <b>—</b> ,       |                                |                |                  |                                       |                     |             |

|          | 0                                                                                                                      |                  | 2 Via on 1                     | Sides          |                  |                                       |                     |             |

|          | Thin Trace                                                                                                             |                  | at Ends<br>Dunting induc       | tance de       | creases          |                                       |                     |             |

|          | Train Trace Fat Trace Mounting inductance decreases                                                                    |                  |                                |                |                  |                                       |                     |             |

|          | <ul> <li>Picture is for reference routing strategy only!</li> <li>→ Critical power plane layer distribution</li> </ul> |                  |                                |                |                  |                                       |                     |             |

|          | For 1V8&3V3: Route on Layer 6                                                                                          |                  |                                |                |                  |                                       |                     |             |

| PCB-014  | eMMC bus and I                                                                                                         |                  |                                |                | rinline conf     | iguration See A                       | nnor 3              |             |

| rCD-014  |                                                                                                                        |                  | es shall be for                | neu III Sti    | ripine com       | igulation. See Al                     | nnex_J.             |             |

| PCB-015 | Minimize the current loop area for the DC-DC converter and keep the switching nodes (SMPS14_SW) as short as possible.                                                                                                                                                                               |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCB-016 | Use a minimum 3 vias per power rail to output capacitor pad for +V_SMPS_1V8 net and minimum 2 vias per output capacitor pad for +V_SMPS_3V3 net.                                                                                                                                                    |

| PCB-017 | The following signals SMPS1_FDBK, SMPS2_FDBK, SMPS3_FDBK, SMPS4_FDBK, are sensitive load measuring signals. Please route these traces as close as possible to the power pins (IC1000&IC2000) clusters or decoupling capacitor areas, in order to dynamically adjust the energy distribution system. |

# **5. Thermal considerations:**

| THERM-001 | A thermal feedback will be provided to the power supply (PMIC) via <b>TH1000</b> (thermistor) to achieve supplementary protection for the controller. In case of overtemperature the supply                                                                                                                                                                                                                                                                                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | rail to the processor will be cut. Make sure that the placement of this component is correct.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| THERM-002 | Since the system will run in space the only cooling mechanism is done using conduction and radiation. In order to remove the heat generated by electronics, one face of the cubical housing will act as a heatsink. Design a planar heatsink having the required radiative surface to dissipate a heat flux of <b>3W</b> . The emissivity of the surface is <b>0.7</b> and the mean temperature is <b>110 degC</b> . What is the thermal resistance of the heatsink? See <i>Annex_4.1</i> . <i>The results must be noted on the documentation layer</i> . |

| THERM-003 | PMIC component has significant power dissipation value. Design the PCB level cooling method (Copper plane, thermal vias cluster and soldermask opening) to extract the heat from component taking into consideration that conduction heat path should have no more than <b>34°C/W</b> thermal resistance. See <i>Annex_4.2</i> .                                                                                                                                                                                                                          |

# 6. Test specifications:

| TST-001 | Test pads must be <b>0.5mm</b> ( <b>0.575mm</b> solder mask opening) in diameter and they must all be accessible for the needles of an In-Circuit Test system (ICT).                  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TST-002 | Test points added for accessing <i>eMMC</i> data/clock lines must be placed on <i>rigid area C</i> , bottom side.                                                                     |

| TST-003 | Global fiducial markers, having circular shape <i>1mm</i> copper pad and solder mask opening of <i>3mm</i> , must be introduced in a proper number, according to IPC recommendations. |

## 7. Fabrication specifications:

| FAB-001 | In order to complete the manufacturing documentation, define one "documentation" layer, |

|---------|-----------------------------------------------------------------------------------------|

|         | which will contain minimum the overall length and width of the PCB. On the same layer,  |

|         | clearly mark the rigid and flexible areas.                                              |

| FAB-002 | The necessary fabrication files (in extended Gerber format) must be provided.           |

| FAB-003 | Distinct drill file for holes must be provided.                                         |

| FAB-004 | Pick-and-place file for all SMT components must be generated.                           |

| FAB-005 | A list of test point co-ordinates must be created, as a text file.                      |

#### Total:

### 300 points